舌尖上的硬件:CPU/GPU芯片制造解析 发布时间:2021-06-30

接下来我们要说的话也许您已经猜到了这张小小的披萨饼中所蕴含的真实,是远不止仅仅是揭示芯片供应链条背后的关系那么简单的。

晶圆厂跟披萨店也有联系?

披萨的美味源自朴实搭配中蕴藏的和谐,更源自整个加工过程的细致规划与悉心投入。我们曾经说过拥有Fab的半导体供应商是“执掌火的艺术”之人,它的努力是半导体芯片能够成型并为我们进行服务的基础,那么小小的披萨背后,能不能体现出半导体工业最核心的部分芯片制造过程的内涵呢?

接下来我们将会向您解密披萨,厄……芯片的制造全过程

在本文章里,您将会看到一幕前所未见的半导体工业图景。CPU/GPU芯片的制造过程,将会在我们烹制整张披萨饼的过程中自然而然的来到您的面前。下面,就让我们开始今天的烘焙之旅吧。

最困难的部分“真正的”半导体工艺

要明白披萨跟CPU/GPU你只整个半导体芯片工业的关系,我们可能首先要面对一点困难的内容比如说,您知道一颗CPU/GPU的基本制造流程么?

晶圆生产线

在不考虑多次掺杂顺序、栅极形成于热处理前还是热处理后以及CMP(化学机械研磨)等细节性问题的前提下,半导体的制作流程大体上可以被概括为这样一个链条:单晶硅锭生长—wafer切割—覆胶—光刻—清洗—蚀刻—清洗—覆胶—光刻—清洗—多次掺杂—多次沉积—芯片切割—封测。

半导体制造过程实际上是一个“自下而上”进行的二维单向过程,人们通过蚀刻形成沟道,透过掺杂形成栅极,经由沉积敷设导线,因为每个过程都需要破坏或者改变一部分wafer表面区域的结构,而且这种破坏和改变都是不可逆的,如果提前破坏了后续步骤需要加工的区域,整个芯片将无法完成。所以半导体芯片的制造必须而且只能按照设计好的顺序,从最底层向上逐级进行这一系列的破坏和改变。

这样的特点,造就了以“覆胶遮盖—光刻—清洗暴露—区域处理”为核心半导体芯片制造的独特过程。

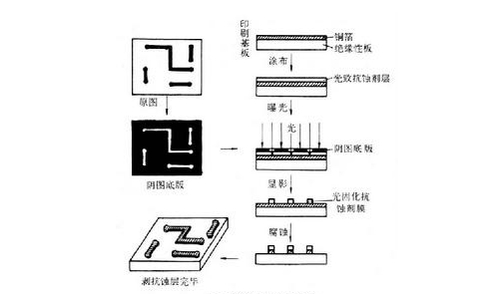

简单的芯片制造工艺流程

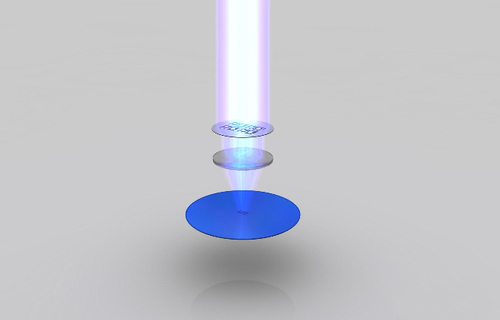

对芯片的加工起点是从最基本的沟道形成开始的,在长成单晶硅锭并切割好wafer之后,我们首先要在wafer表面敷上一层对特定波长光线非常敏感的溶胶。接下来,我们会用事先标记好需要形成沟道区域位置的掩模作为“底片”对覆胶表面进行特定波长光束的照射,这一过程就是我们所常说的“光刻”,所有被光束照到的溶胶都会发生光化学反应并产生性变,清洗会令其脱落并暴露出需要蚀刻的wafer表面。

光刻过程

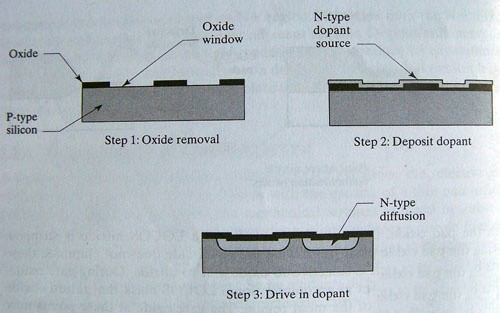

在这些暴露的表面通过蚀刻完成沟槽的侵蚀“开挖”之后,我们需要清洗并去除wafer表面残存的对非沟道区域起保护作用的溶胶,然后在完成一次“覆胶—光刻—清洗”的过程,只不过这次被暴露出来的位置是需要透过渗透掺杂来形成栅极的区域。接下来,我们会根据不同需求以及不同Fab的特点多次完成注入/扩散掺杂过程,以此来创造出不同的电学特征区域,也就是形成栅极。

接下来需要进行的步骤是完成互联,无论是使用CVD还是PVD手段,在现有的铜互连工艺当中,我们都会在需要敷线的空间中事先预留好空白和保护区域,然后将接触材料(在铜中毒敏感场合使用的其他金属材料)以及铜以气相沉积的形式扩散进区域并沉积形成导线。至此,芯片的制造主体过程大体上就算完成了,在经过切割和封装测试之后,它就成了我们所熟悉的半导体芯片。

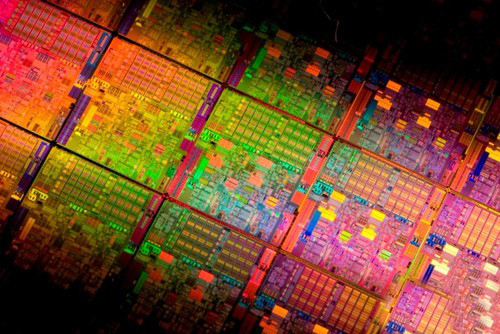

制造完成等待切割的芯片

当然,这样的过程并不是一上手就可以成功的。依旧受“自下而上进行且不可逆的二维单向过程”影响,整个半导体工艺过程中的每一个步骤都会对后面的步骤产生影响,这种影响不仅造成了下游效应这一影响芯片良率的现象,更让半导体制造变成了一个需要多次学习和经验积累的过程。这样的学习过程就是我们通常所说的tape out/retape out,也就是多次流片过程。通过多次流片并观察和调整工艺细节,最终成型的工艺将会被用来部署在流水线上进行批量化的快速芯片加工,但被调整的部分均属细节,整体步骤通常依旧会维持我们前面所接触的这一顺序来进行。

晶体管可不是“管”哦

在看过半导体芯片制造的大体流程之后,我们需要明确几个容易出“状况”的地方,这些小问题不仅产期困扰了很多的爱好者,还在认知层面给我们带来了许多的误区。想要理解CPU/GPU究竟是怎样制作出来的,这些小问题需要被首先纠正。

1、半导体工艺经常会提及“光刻”工艺,但绝大部分“光刻”并不像很多人想象的那样用硬X射线、强力激光、中子波束、1096beam或者黑龙波什么的在晶圆上直接以轰杀的方式挖沟拓渠。除很少一部分直接激光通孔之外,光刻工艺所“刻”的都不是wafer本身,而是wafer表面的覆胶。它的目的是让需要形成被加工的晶圆部位“露出来”,以便后续的蚀刻、掺杂、沉积等工艺的开展,并让不需要被加工的地方继续为覆胶所保护。

晶体管可不是“管”哦

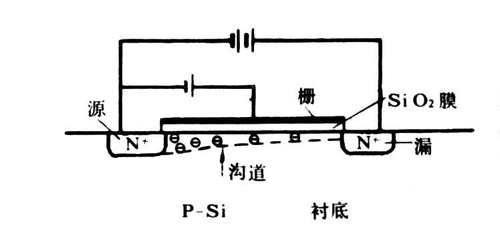

2、“晶体管”并不是“管”,更不是用一把小镊子夹起来再插到wafer表面的。微观电路中被我们讨论的晶体管尽管具有本质上与早期的晶体管完全相同的电学特性,但它早已经不再是矗立在包覆电极的一大坨晶体那样的尊荣了,实际上我们可以用“特殊电学性能区域”来称呼平时被我们叫做晶体管的那个东西。如果要对栅极的形象进行描述,它其实就是wafer表面的一小块凸起或者凹陷,经由在其周围掺杂而具备了特定的电学特性,再借由栅极形成控制机制来达成对开关的控制,可以达到“晶体管”相同的功能和作用。

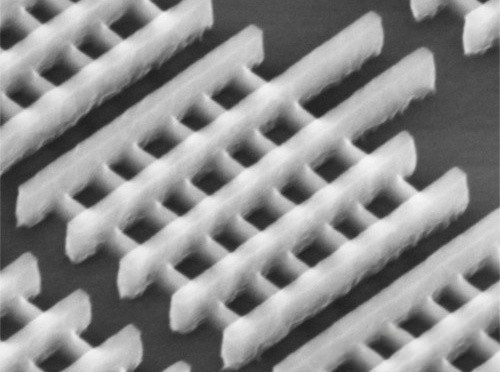

3、“XXnm工艺”所说的并不是晶体管或者说栅极的尺寸,这里说的是刻线宽度,亦即光刻过程预设的沟槽的宽度。

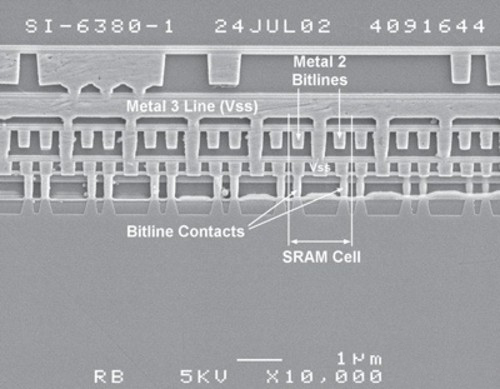

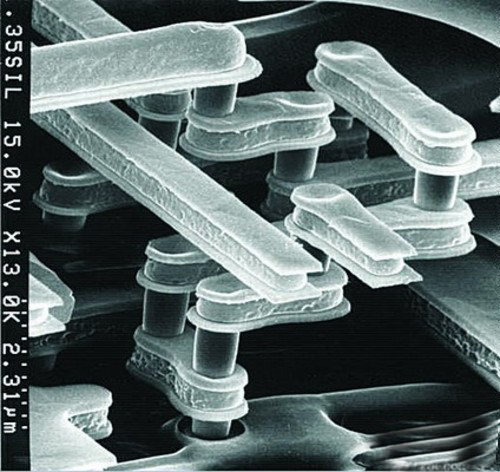

4、芯片并非只有一层,因为需要大量以公里为单位计的微观连线,芯片需要在栅极所在的逻辑层之上完成多达6~8层甚至10层的金属层,这些层被用来以空间的形式完成导线和互联,这就是我们常说的多层互联工艺。原则上互联层空间利用越有效,导线在逻辑层中出现的距离和所需空间也就越少。因此,优化互联方式或者直接上攻互联层都有助于芯片面积的减小以及功耗的控制。

多层金属互联

好吧,我们知道整个芯片的制造过程多少有些难以理解。所以我们还是继续原本就要进行的工作烤披萨饼吧。在了解了一份美味的披萨从原材料准备到最终出炉瞬间的全过程之后,相信您将会对半导体芯片的制作过程有一个全新的认识。

制作“wafer”和面

要烘焙一张松软可口又浓香满溢的北美烤盘披萨,最基础的事自然是制作饼胚了。和面是一个将面粉变成面团的过程,从本质上来讲,这一过程跟准备wafer是没多少区别的。

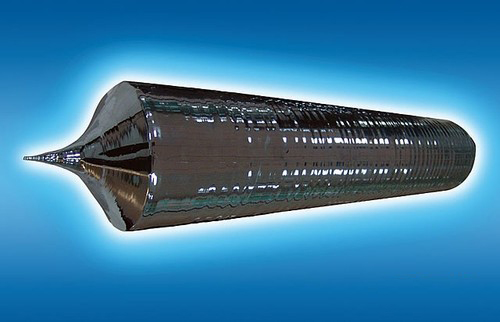

一切的起点单晶硅锭

面粉本来是分散的淀粉/蛋白质分子团所构成的颗粒,通过适度水的作用,面粉中的蛋白质和淀粉形成了网格状的长链形态,从而促成了面粉从颗粒向团聚的转变。光有水是不够的,面粉变成面团还需要施加适当的外力来帮助过程的进行,我们揉面的过程可以让水更加均匀的进入面粉,还可以促使长链更好的形成网格并增强面团的弹性。所以揉面是一个细腻而且充满了艺术的过程,水的多少、揉压的手法和力道、甚至是醒面和擀制面胚的步骤都需要精心对待。

cookies needs love like everthing does

我们高筋面粉加混合了干酵母的温水来揉面,同时为了让面饼更加松软清香,我们还在其中加入了适量的黄油。黄油的加入增加了和面的难度,所以我们用了比平时更多的时间去揉压、锤捣和醒发,力求让面饼达到最佳的状态。虽然过程费时而且相当消耗体力,但为了可口的美味,这样的消耗是值得的。活好面之后,我们把它擀制成与烤盘尺寸相仿的大小,并在上面打一些小洞,一块披萨的面胚就算准备完成了。

可爱的面团已经搞定,只等擀成面饼了

单晶硅的生长也需要经历一个类似的过程。单晶体生长是一个平衡延展的过程,任何杂质、应力处理不当或者不均匀的热力学起伏都可能诱发缺陷以及对称破却,并导致晶格变形的发生,让硅晶格从有序对称延伸转变成无序或近程有序状态,进而让单晶硅变成多晶硅。所以硅被熔融提炼之后,晶胚需要在一个严格控制温度及其他要素的纯净环境中完成冷却生长过程,一直到单晶收尾都是如此。稍有差池,整个单晶硅锭都可能会报废。成长完成之后,经过高精度的切削加工,被切成片的单晶硅就成了我们所说的wafer,也就是晶圆。

Cookie needs love like everything does,只有用心去对待,我们才能获得自己想要的完美的结果,不管是和面还是制作单晶硅都是如此。

覆胶,光刻融化的奶酪

在面胚准备好之后,我们要做的下一步工作就是将番茄酱、奶酪以及其他各色食材码放在面胚上面,这个混合食材的过程,在形式和意义上都非常接近半导体芯片制造过程中的“覆胶光刻”过程。

“覆胶光刻”过程

以披萨的角度来讲,番茄酱抹在最靠近面胚的地方不仅可以为披萨带来酸甜的底味并为后续的味道混合增加层次,同时还可以防止面胚水份和内部气体的过快流失,这有利于面胚充分膨胀以及维持松软的口感。同样的,奶酪的放置同样由这样的作用。在水分散失最快的加热烘焙初期,奶酪的融化并不充分,这种不充分刚好可以覆盖面胚并阻止水分向上蒸发。这种特性,让番茄酱和奶酪发挥出了“覆胶”类似的作用。

我们使用的“上层覆胶”瑞士干奶酪

我们在前面的文章中提到过,“覆胶光刻”过程的操作细节和目的在于暴露需要加工的wafer区域,同时保护不需要加工的区域。因为蚀刻并不具备自主选择性,必须加以约束才能达到定向加工的目的,所以覆胶之后,我们只需要对需要加工的区域进行照射,接着只剥离因反应而性变的胶体部分并暴露下方的wafer区域,就可以达到为下一步的蚀刻提供“渠道”了。

覆盖、保护、为后续步骤提供基础和前提,甚至都还没有送进烤箱,披萨就已经表现出了如此多的与半导体芯片加工过程相似的环节和特征,我们不得不钦佩大自然的神奇即便看似毫不相干的两个领域,其内在往往也是受同样的规律所支配的。

敷好了番茄酱、奶酪和馅料,还顺手完成了“覆胶光刻”的过程,那么当我们将披萨送入烤箱之后,是不是就该看到沟槽形成了呢?

沟槽形成受热膨胀的发面

随着面饼被放入烤箱加热,一系列神奇的变化都将会开始陆续发生,这其中首当其冲的就是发酵面饼的膨胀。

发酵工艺是人类利用微生物的成功典范之一,它会在适宜的温度下吞噬淀粉,利用淀粉酶将淀粉分解为麦芽糖并进一步分解为葡萄糖,然后以无氧呼吸的方式将至消耗并生成酒精和二氧化碳的,数千年来酵母菌都在忠实的完成着让面饼变得松软可口的任务。由于我们使用了添加酵母的温水来和面,酵母菌会在面胚内部释放了气体,这些气体在受到烘焙过程的加热之后就会膨胀并在面胚中形成一个个的小孔。这些小孔不仅会让面饼变得松软,还为后续汤汁的下渗混合提供了场合。

发酵是披萨美味融合的前提

作为半导体加工工艺的重要步骤,沟槽的形成同面胚中的气孔有着异曲同工之妙。无论是形成PN结还是用于敷设线路,沟槽在半导体上芯片中都扮演着重要的角色。在经历了先前的“覆胶光刻”过程之后,wafer表面已经露出了所有需要形成沟槽的区域,人们接下来所进行的工作,就是利用这些没有覆胶区域所形成的“沟渠”,通过物理或者化学侵蚀手段来完成这些区域内不同深度的沟槽开挖工作。覆胶的沟渠起到了导向的作用,可以让侵蚀沿人们规定的方向定向进行,而覆胶本身尤其到了保护待加工的作用。

沟槽对PN结非常重要

面胚已经膨胀,wafer的表面也已经完成了沟槽的加工,那么接下来,我们又会遇到些什么呢?没错,无论是披萨还是半导体芯片,这时候都该是时候“掺杂”了。

掺杂,沉积汤汁的下渗和馅料混合

顾名思义,掺杂就是在原本“纯净”的基体表面及浅表以渗透的形式加入原本没有的东西。在半导体芯片的制作过程中,掺杂就是通过物理化学手段将归于硅以外的元素注入到wafer浅表,而对于披萨而言,“掺杂”就是各种食材馅料出汤之后下渗混合的过程。

随着烘焙过程的进行,我们敷在饼胚表面的各种馅料都会因受热和出汤。无论甜椒、洋葱、培根还是草菇,它们本身独特的香气都会伴随着汤汁从本体里渗出,我们最终所要收获的正是这些香气混合所产生的味道。而让这些蕴含香气的汤汁充分混合的场合,就是披萨的“掺杂”过程。

这么多材料可不是白准备的

随着馅料中汤汁的渗出,自然重力让这些汤汁均匀的下渗到了奶酪和番茄酱所在的位置,而随着烘焙时间的延长,奶酪已经随着烘焙热量的增加而融化的更加充分,可以与下渗至此的汤汁以及下层的番茄酱更好的混合了。与此同时,饼胚的膨胀在此时也在同时进行当中,气孔形成的空间刚好接纳了自上层下渗的混合了番茄酱、奶酪、肉菜以及草菇的浓汤,至此,在被汤汁渗透的面胚中,美味已至。

烘焙的加热是汤汁渗出的关键

“半导体”本身并不是一个严谨的翻译,实际上我们可以将之理解成“电流只能在特定条件下定向单向流动”的特殊导体。半导体的导电并非像正常金属导体那样以电子气体定向移动的形式来完成,它必须经由硅晶格共价键空穴的载流子定向迁移过程来完成,其性能亦由此决定。而掺杂过程的作用,就是通过混入其他元素来改变硅晶格的结构,进而大幅改变局部区域的电学性能。一旦某一区域的电学性能达到了人们的要求,并且形成了以栅极为形式的控制开关,我们就可以将这一区域看做是“晶体管”的存在了。

掺杂形成N结

同披萨汤汁的下渗一样,掺杂同样是一个物质下渗混合的过程。再又一次的覆胶光刻过程之后,氧、氮、磷、硼等等元素按照人们的需要被带入到了特定的裸露出来的区域当中,并在不同扩散驱动力的作用下深入到了wafer的表面。元素的渗入改变了被渗入区域包括电阻以及电容量在内的大部分电学性能,让该区域成了有别于基体的可以为人们所用的半导体结构,再加上沉积形成的栅极,一个“晶体管”就算是完成了。

我们想要运算能力,于是我们发明了掺杂沉积形成的晶体管,我们想要美味,于是我们找到了各色食材完美混合的方式。努力去拾起更多大自然给予的馈赠,也许就是我们生存至今并仍在不断发展的原因吧。

上层互联软糯的馅料

汤汁并不是馅料的全部,各种食材独特的口感也是构成食物本身吸引力的特征之一。披萨的吸引力除了混合在一起的平和美味之外,还有上层馅料交织在一起的饱满口感。

烘焙15分钟之后,该“上层覆胶”了

由于我们采用了两种不同的奶酪,其中流动性较差的瑞士干奶酪会在烘焙15分钟之后才加入到馅料的最上层,因此随着烘焙过程的继续,位于饼胚上层的馅料会与瑞士干奶酪逐渐混合并形成一个整体。干奶酪的嚼劲搭配蔬菜、培根和草菇各异的口感,让我们在品尝美味的同时体会到了进食的快感,并最终在我们的舌尖形成了披萨丰满的形象。

芯片中的互联

半导体芯片的制造同样要经历这样的过程。无论是CPU还是GPU芯片,布满晶体管的逻辑层都需要与外部电路进行对应的连接。动辄十数亿甚至数十亿的晶体管总量显然是一个非常庞大的数字,将它们连在一起的连线长度也是相当可观的。要布置这些连线,而且同样是“自下而上”不可逆的单向布置这些连线,我们需要的是一个复杂的多次沉积过程,通过各种保护和气体扩散,将金属元素以PVD(物理气相沉积)或者CVD(化学气相沉积)的方式扩散到了特定的区域,并在该区域形成连线,这就是互联形成的过程。有了互联,芯片才有了存在的意义和工作的基础。

第一张饼出炉喽

“叮”,随着烤箱时间转盘的归零,一份令人期待的披萨就这么出炉了。

tape out和retape out烤砸了,那就调整吧

生活经验告诉我们,这世界上不可能有永远一帆风顺的事。当外部环境发生变化之后,一些原本顺利的事可能会变得不顺利,半导体芯片的生产过程会随着设计、工艺需求以及生产线技术的改变而遇到困难,厨子也会因为灶台和厨房空间的变化而把菜搞砸。

厄,好吧……我们承认我们制作的第一张披萨可以说完全失败了。

别看料足,二号披萨最终失败了……

由于家电评测室内的室温过低,发面过程进行的相当不顺利,酵母菌们一直都在沉沉的睡去,面饼也始终没有按照我们的需求充分的膨胀起来。我们的菜单以及上下均温的烘焙方式都是针对出汤混合的北美烤盘披萨的烹制过程设计的,没有充分膨胀的面饼无法吸吮大量渗出的蔬菜汤汁以及融化的奶酪,底盘温度不足又让面饼改变松软的形态,无法隔绝汤汁的下渗,于是我们的第二张披萨成了由大量浓汤浸泡的死面,几乎变成了一盘鱼头泡饼……

没办法,赶紧修改工艺吧同志们,要不中午饭可就要“泡汤”了。